# Energy Efficiency in the Al Computing Era

The Future of Power Delivery Inside the Processor

F. Carobolante, Intel Corp.

## A Journey

- "What got us here won't get us there"

- One size doesn't fit all

- Looking into the crystal ball

## A homage to Intel – 20 years of research in PwrSoC

- Ted DiBene "Power on Silicon with on-die magnetics"

- Dominik Schmidt "Challenges and Solutions: Power Delivery and Regulation in NanoCMOS SoCs"

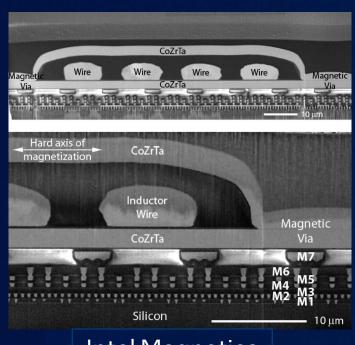

- Donald S. Gardner "Integrated On-Chip Inductors Using Magnetic Material"

- Ted DiBene "Fine Grain On-die Integrated Magnetics; Breaking the Power/Performance Barriers"

- Rinkle Jain "Enabling Aggressive Dynamic Voltage and Frequency Scaling in Many Voltage Domains"

- Mondira (Mandy) Pant "The Era of Intelligent Power Delivery"

- Rinkle Jain "Distributed Power Conversion An Answer to Power Delivery Challenges in SoCs?"

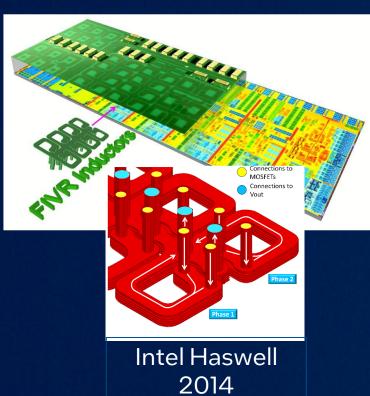

- Amit Jain "FIVR Control topology and design for distributed loads".

- Christopher Schaef "Potential of Hybrid Converters in Compute Platform Powers Delivery"

- Rinkle Jain "Fine Grain Voltage Domains on Graphics"

- Ravi Mahajan "Advanced Packaging Architectures for Heterogeneous Integration".

- Vivek De "System-Level Power Management Strategies for Integrated Platforms"

- Ravi Mahajan "Advanced Packaging Architectures for Heterogeneous Integration

- Kaladhar Radhakrishnan "Magnetic Inductors for Next Generation IVR".

- Han Wui Then "GaN-on-Si Process Featuring GaN MOSHEMT Transistor Technology a Integrated Silicon CMOS on 300mm Wafers"

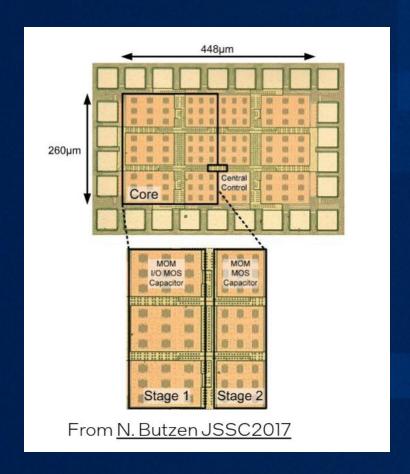

- Nicolas Butzen "Next-Generation Switched-Capacitor Converters using High-Density MIM Capacitors"

## The Challenges

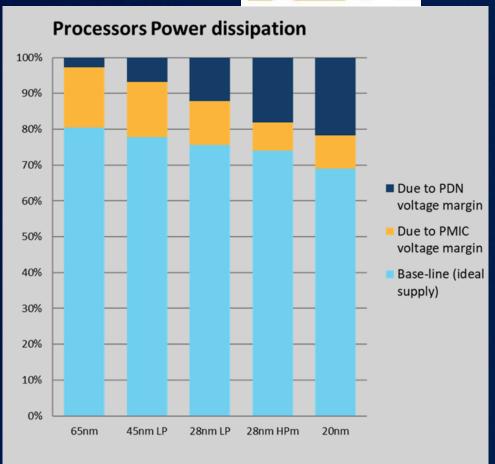

## The 1,000 A challenge

System Vmin

Guardband

Overdrive Control Frequency

**Vt Variation**

Threshold Voltage (Vt)

For Leakage Control at 100°C

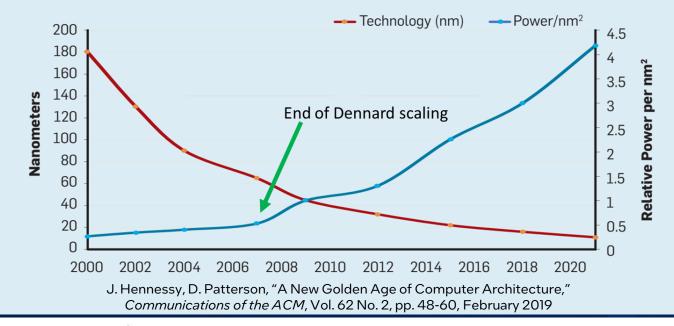

Power increases by 3% for every 10mV increase in supply voltage!

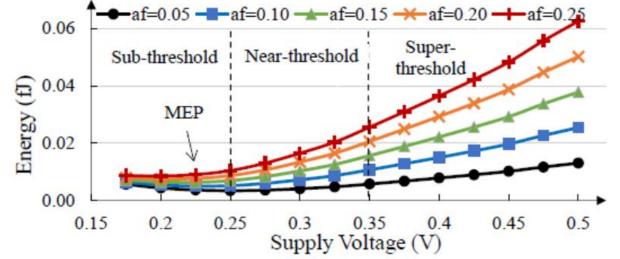

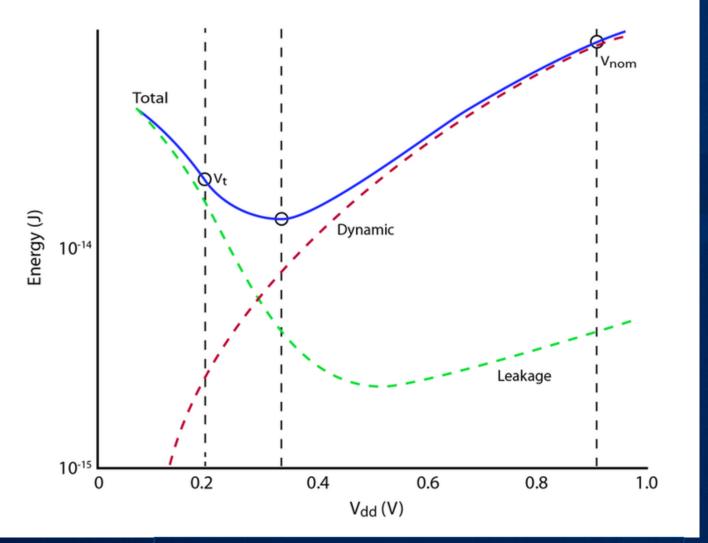

Figure 4. Energy consumption of a 20-stage inverter chain versus supply voltage at different activities factors (af) for FinFET 7nm normal  $V_{th}$  device.

**CPU Voltage**

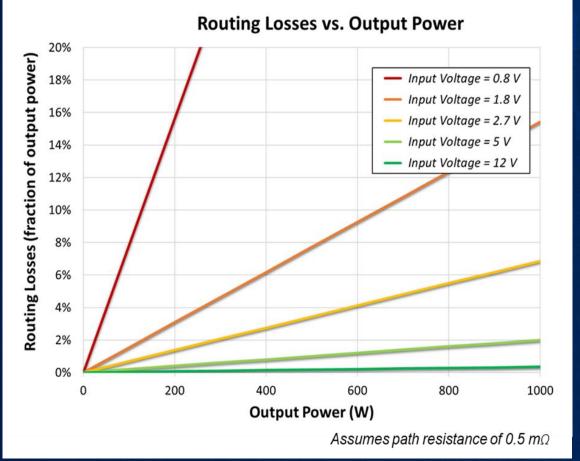

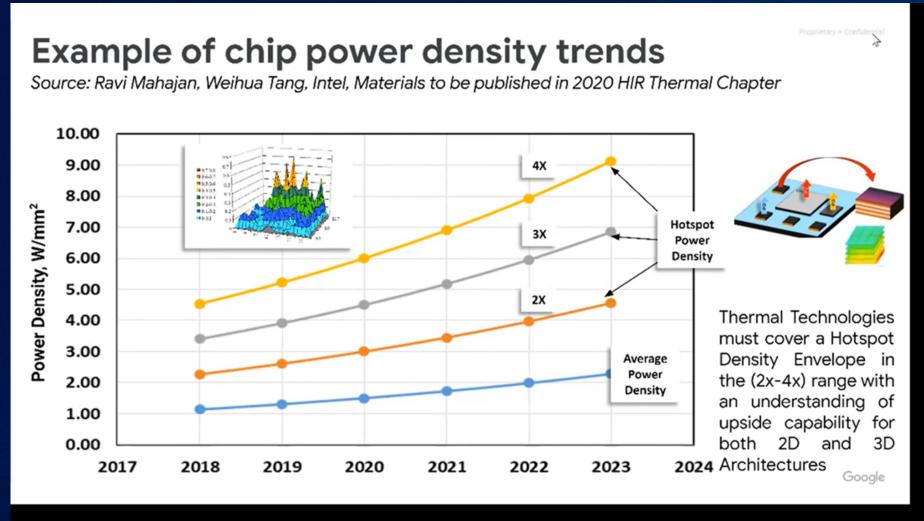

## The snowballing effect of high current and power density

#### F. Carobolante

#### K. Radhakrishnan

## When you have a single stage conversion...

## **PWR** 18

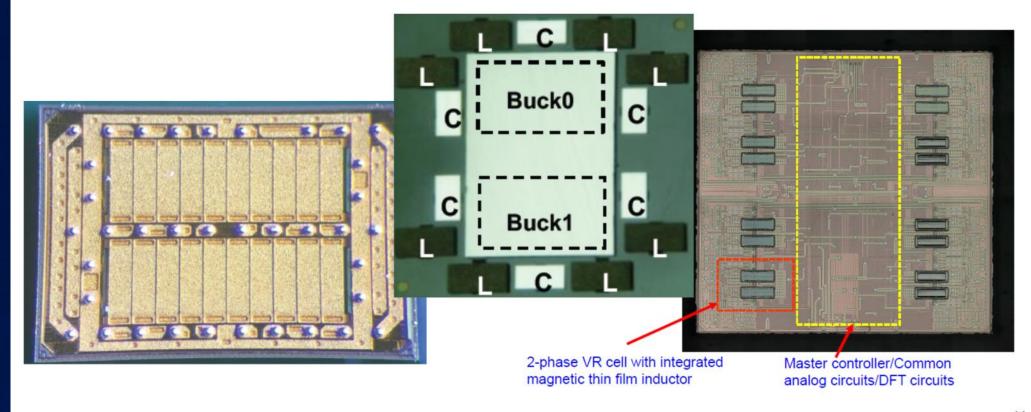

## Ferric, Dialog and Huawei show fully integrated PwrSoC's

14

F. Carobolante "PwrSoC at an Inflection Point From R&D to Market Relevance" APEC 2021

## A Few Key IVR Milestones from Intel

Intel Magnetics on Silicon 2008

Intel @ PwrSoC 2021

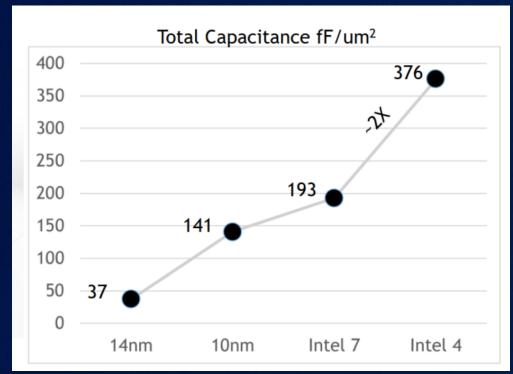

## \*Good\* capacitors are your best friends

- Deep Trench... not compatible with transistors

- MIM caps: achieving high density!

From https://www.semiconductor-digest.com/intel-4-process-drops-cobaltinterconnect-goes-with-tried-and-tested-copper-with-cobalt-liner-cap/

### Need a Doctor? Dr. GaN [GaN Research at Intel]

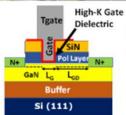

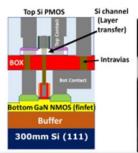

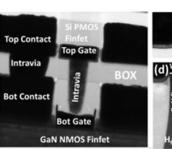

#### 300mm GaN-on-Si(111) Process

Power GaN Die (W=1000mm)

- 300mm Si (111) HR substrate

- High-k E-mode MOSHEMT

- Schottky GaN HEMT

- Min channel Lg 30nm

- Regrown N+ Source/drain

E-mode high-K GaN Transistor

## V3 ILD V3 M3 M3 M2 V2 M2

**Backend Metal Interconnect**

Passives: inductor, MIM and TFR

#### **Circuit Research**

- Power electronics

- Sub-7Ghz Doherty PA

- 28 40 GHz PA, LNA

VLSI '21, '22

#### **GaN and CMOS Integration**

IEDM '19, '21

Han Wui Then "GaN-on-Silicon Process Technology" PwrSoC 2023

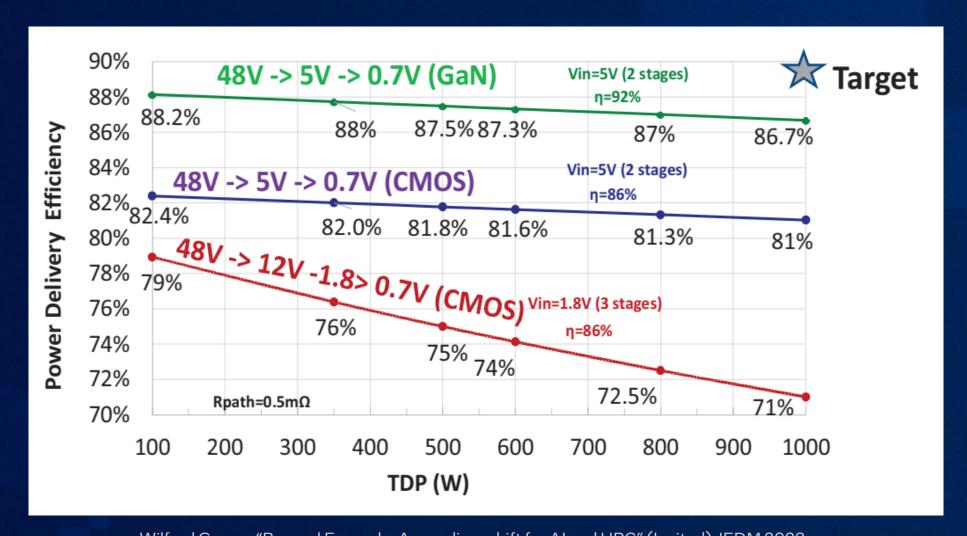

## Efficiency projections

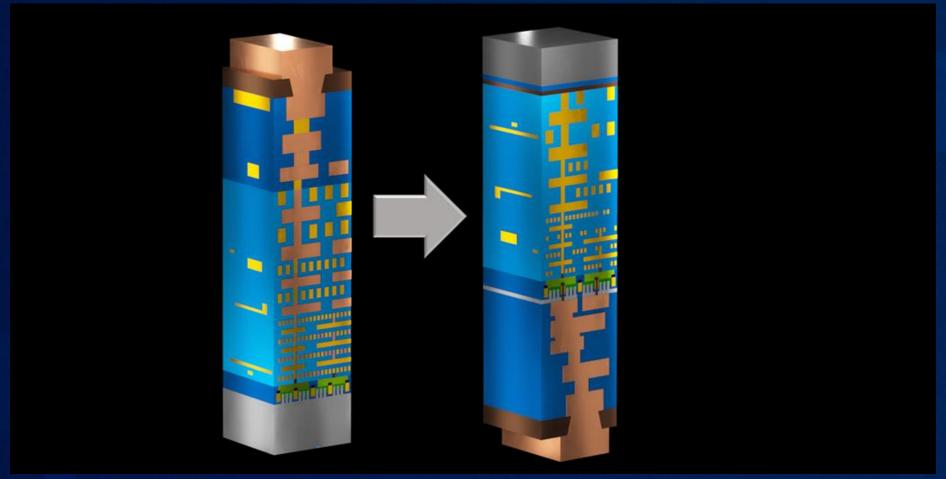

## Now: Chiplets and Heterogeneous Integration

A STATE OF THE PARTY OF THE PAR

- 47 Tiles

- Five Process Nodes

FOVEROS and EMIB Integration in the same Package

Rambo Tile

Foveros

Base Tile

**HBM Tile**

X<sup>e</sup> Link Tile

Multi Tile Package

**EMIB** Tile

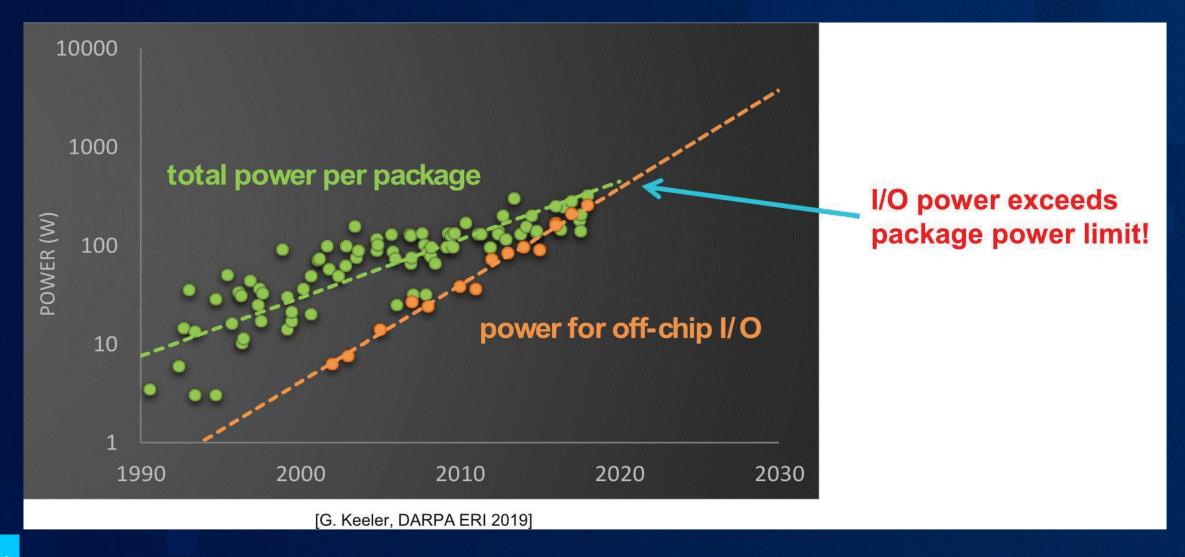

## ...and the need for integrating Optics

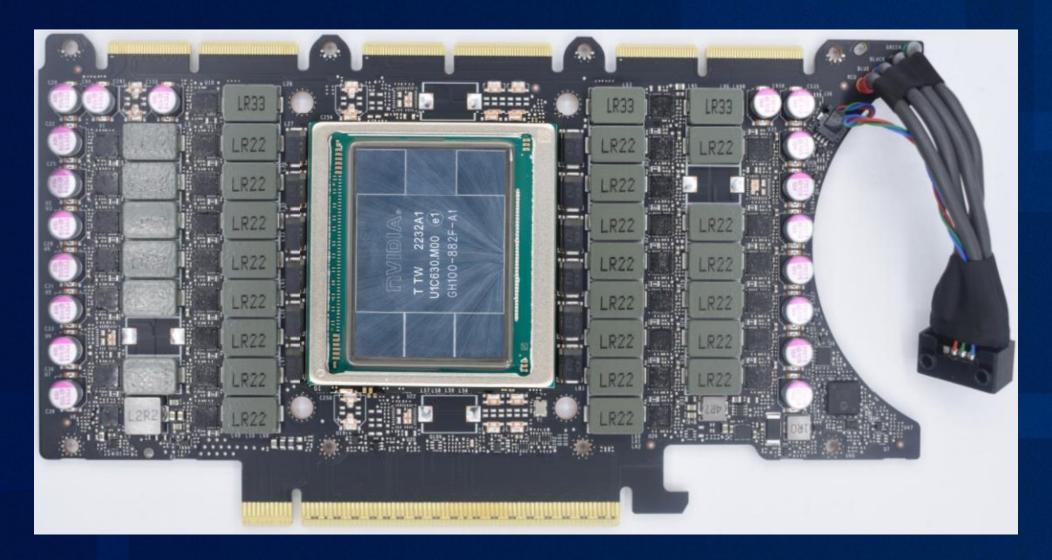

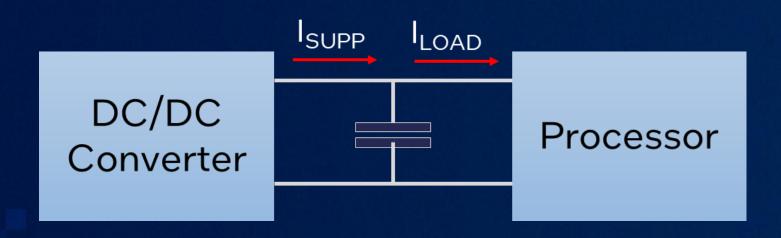

#### CPU Vs. GPU

#### **CPU**

- High Peak-to-Average ratio

I<sub>SUPP</sub> = I<sub>LOAD\_AVERAGE</sub> << I<sub>LOAD\_PEAK</sub>

- Unpredictable loads

- Hot spots limited

#### **GPU**

- Sustained high current  $I_{SUPP}$  approx. =  $I_{LOAD}$

- Predictable loads, but...

- Thermally limited

## Fine-grained power delivery & load balancing

## Liquid immersion cooling

https://www.intel.com/content/www/us/en/newsroom/news/intel-dives-into-future-of-cooling.html

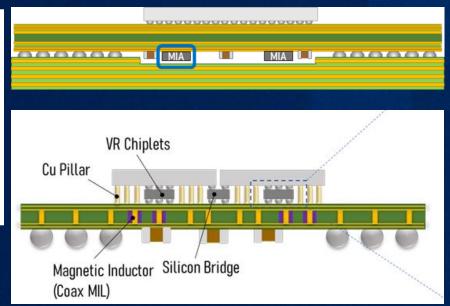

## Optimizing both Signal and Power Integrity

R. Mahajan, Advanced Packaging Architectures for Heterogeneous Integration, PwrSoC 2021

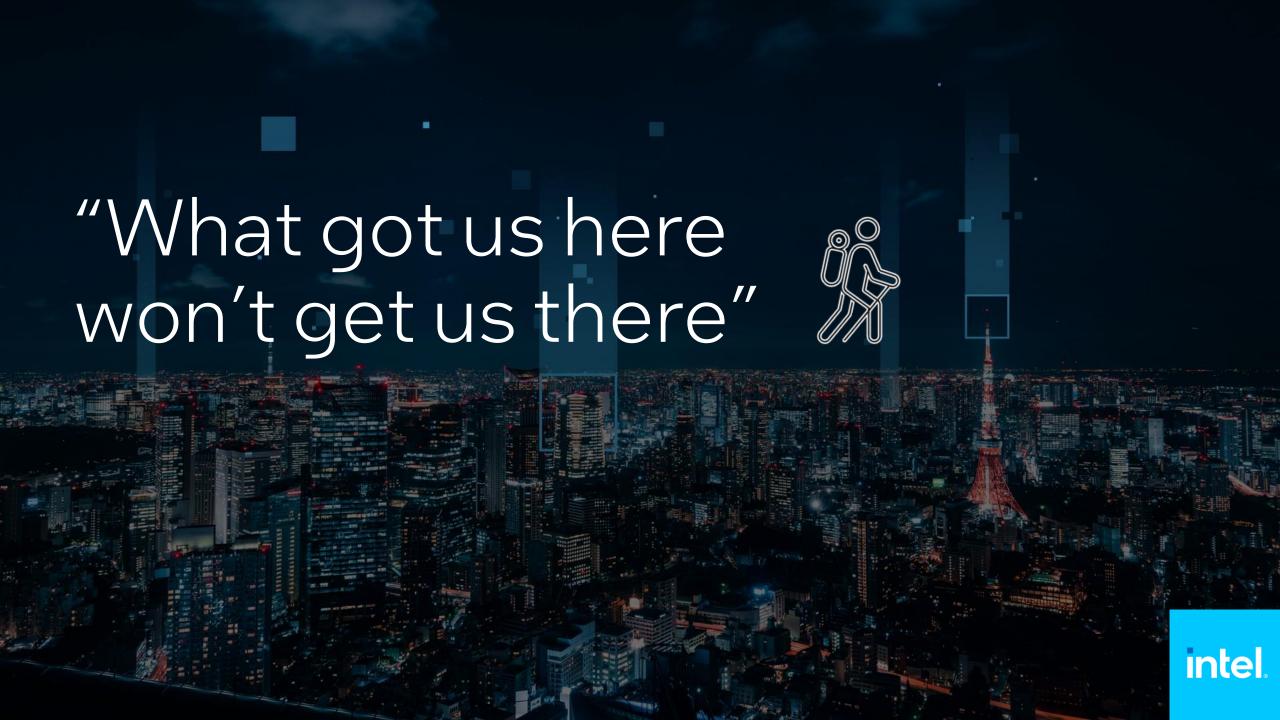

## What about Al

- Proactive Power Mgmt with ML

- Security

Looking into the crystal ball

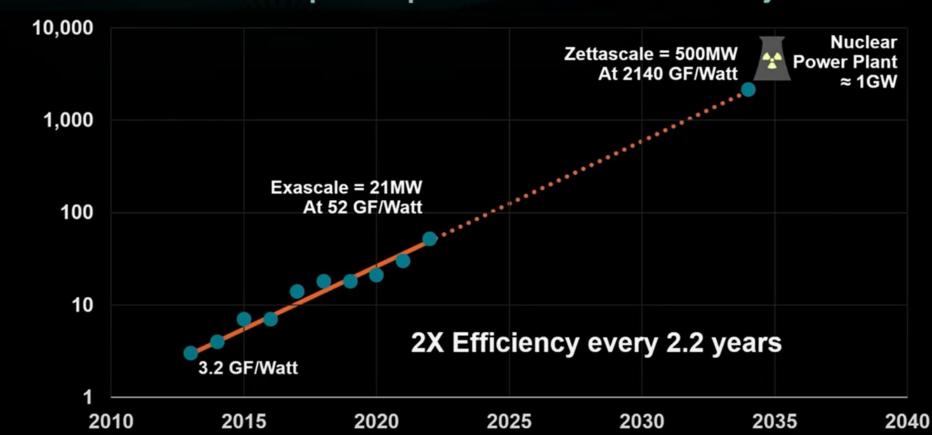

Green500 Supercomputer GFLOPs/Watt and Projection

Lisa Su ISSCC 2023

12 © 2023 IEEE International Solid-State Circuits Conference | February 20, 2023

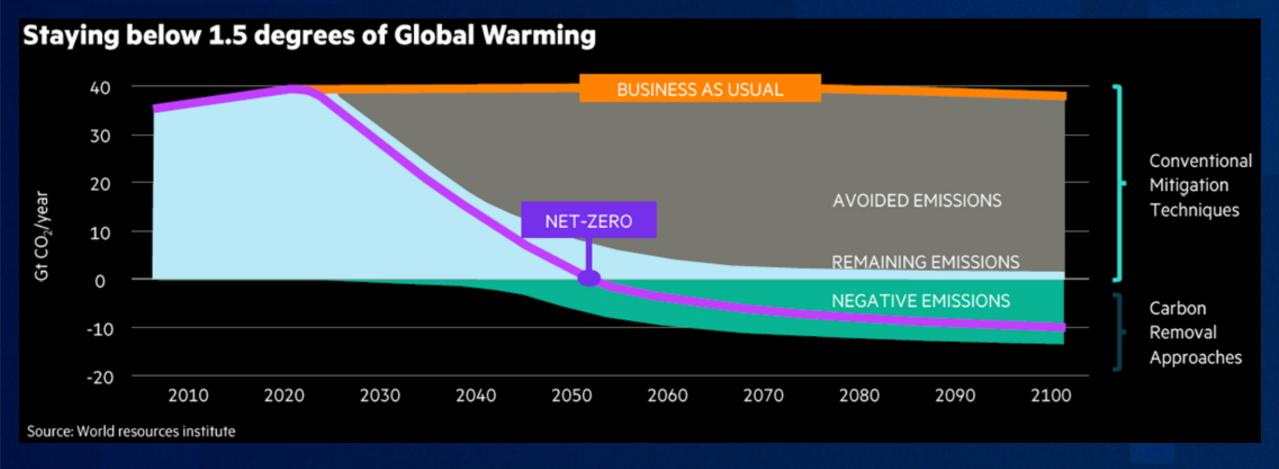

### The Sustainability Challenge... Many are working on it!

DOE EES2

## CMOS Operation Close to Threshold... not a solution!

- Theoretically, you can optimize efficiency, but...

- Minimum core voltage limited by circuit functional and timing failures from process variation and noise

https://www.techdesignforums.com/practice/files/2014/05/variability.png

## Our brain: massively parallel at low power

- Neural Network based architecture

- Beyond CMOS transistors

### Questions?